This time, it's said. I close the topic 'µPF--1 clone'

Why? Because it works.

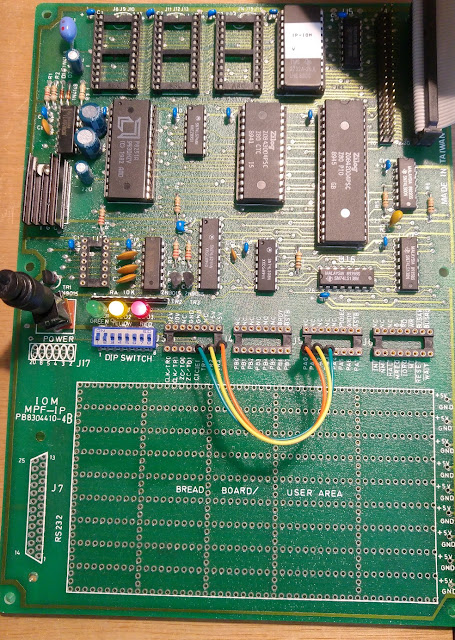

A few years ago, when I set out to attempt to replicate Wichit Sirichote's work in FPGAs, I developed a minimal system based on the sources of Wichit Sirichote. It had already taken me quite a bit of time to translate all the hardware onto a commercial FPGA board, then develop a personal board to accommodate an FPGA module. I found that it would have taken me too long to re-write a complete system based on poor quality of the source provided.

And then, I wanted to test the GoWin FPGAs. When I say testing, I mean creating an FPGA board and then programming a complete system. That is to say also test the GoWin development tools.

|

| Free advertising ;-) |

After seeing that the small computer created 'seems' to work fine. I decided to attack what is the center of interest of such a small computer, namely the operation in step by step.

Until then, I had contented myself with re-writing the source of Wichit Sirichote to allow the manipulation of addresses and data as well as the loading of programs by serial link. So I missed the step by step. In terms of real learning of processor operation, step by step is extremely interesting!

It's quite interesting to be able to modify a program value almost on the fly, then to check the result by immediately restarting the program. That's the whole point of such a computer.

It's a personal opinion, but I find it much more relevant than working on Arduino modules as a discovery of computing.

The system set up for step by step operation is based on an interrupt triggered after a certain number of pulses of the signal M1. Interesting and very functional system. On this point, Wichit Sirichote's source served me well.

So there you go, I have everything set up except the 'REL' key. I couldn't figure out its usefulness, even studying the provided source well. Regardless, it is now possible to write an entire program by directly entering the processor codes, or more simply by loading the program via the serial link and modifying the code directly on the keyboard, starting then stopping the program to check the content of processor registers etc etc...

Small example of a program loaded via the serial link:

The system is therefore validated. The GoWin FPGA used works perfectly. It is a success. I forgot, the serial link works perfectly, here at 115200 Bauds, and not faulty at 1200 Bauds as on Wichit Sirichote's system ;-)

In terms of FPGA resource usage, this is what it looks like:

Barely more than half of the resources in logic gates. I haven't implemented expansion port management, but it only takes a few dozen logical units. Not bad at all!This machine may have come out too soon...

|

| Free advertising ;-) |

I am really impressed with the quality of his work...

It seems to work. Why do I say 'seems'? Because I don't own thermal paper. So I can not check if the message is printed correctly. All I can say is that the printer responds correctly to requests made through routines present in the ROM integrated onto the printer board.