At the moment, I'm still stuck on what I think is the main problem, which is a supposed malfunction of the SIO/2 which manages data writing and reading from the floppy disk drive.

The SIO has two serial ports numbered #0 and #1.

So I created a small monitor for the EMU1 mother board from port #1 of the SIO, allowing me to run the RAM test, because the EMU1 has an original serial output available for external communication with a computer.

I had a lot of difficulties making this monitor. But, after a while, it ended up working on port #1 of the board's original SIO/2.

Then, I tried to make this monitor work with an SIO/2 which I assumed was fully functional. I never managed to get anything. Hence the doubt about the functioning of this other SIO/2.

In fact, I ordered five more SIO/2s, directly from a supplier in China. Supplier from whom I sometimes order unobtainable components, and with whom I have never had a problem.

So I tested my monitor with these five new SIO/2s. I never managed to get anything. And the EMU board didn't show any more signs of working when I booted it with the stock OS. Hence, once again, the doubt about these five new circuits.

Result: I went in two directions simultaneously. The first to consist of purchasing two SIO/2 again, from Germany this time, then creating a small adapter board allowing a SIO/2 to operate in place of a SIO/0. The difference between these two components is minimal and consists of just two or three port #1 pins to rearrange. There is no differences in software.

The adaptation circuit that I sent to be made:

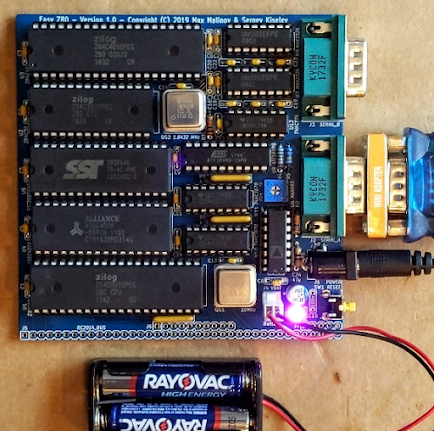

I actually intend to use a small computer board under CP/M 80 which has a SIO/0 in order to test the operation of the two ports of all the SIO/2s in my possession. This is the Easy Z80 board created by Sergey Kiselev and available on his github repository: https://github.com/skiselev/easy_z80

I built this board in 2021. Since then, the RomWBW ROM has gone from version 3.0.1 to version 3.4.0, with the possibility of swapping the monitor's communication port using the simple command "i 1 115200" for example. I told myself that I had a perfect system for testing my SIO/2s.

First of all, I updated the ROM of this little system, and tested the controls with the original SIO/0 circuit. And indeed, at startup, I have communication with port #0 of the SIO, then after launching the command, communication goes to port #1. This part being validated, I therefore inserted the SIO/2 to SIO/0 adapter on this Z80 board and started my communication tests again.

|

| My Easy-Z80 with an SIO/2 on my adapter. |

|

| Eazy-Z80 currently on port #0 asking for going to port #1 |

|

| Easy-Z80, communication established on port #1 |

And there: amazement!

All SIO/2s in my possession, other than the original one on the EMU1 board, work. Which embarrassed me. This means that there is a problem, either in the initialization of the SIO which I do in my monitor program, but then, why it works very well with port #1 of the original SIO/2? Or there has an electronic problem on the EMU1 board, which I cannot determine. And again, why does this work with the original SIO/2?

On the other hand, and this is very good news, I was able to notice that on the Easy Z80 board, the original SIO/2 whose port #1 works very well on the EMU1 board, does not work correctly, in any case on its port #0. The transmission goes without problem, I get the board's monitor pattern every time I perform a RESET of the board. On the other hand, I only receive characters very rarely, and when it goes well, it is only a few characters maximum and only on the condition that the board has just been put back under power. In fact I got exactly the same result when I coded my monitor program not to work with port #1, but with port #0.

So, there, I can now conclude that the original SIO/2 of the EMU1 is not working correctly and, in its current state, is in any case incapable of receiving information from the floppy disk :The TX function of port #0 therefore seems to work normally, however the RX function only works a few seconds after powering up. That's already a good point.

The second thing now is to try to understand why none of the functional SIO/2s are able to provide me with access to the monitor that I programmed for the EMU1 board. Signals problem or problem in my code?

I feel that the origin of the problem may not be easy to determine...

Small remark about the Easy Z80 board. I am completely surprised that RomWBW is still maintained and even improved four years after creating this little system. It's actually quite cool to see this board working in a terminal on my PC. Guaranteed vintage feeling...